# IX3407B

Single-Channel, Isolated IGBT Gate Driver with Separate Outputs

#### **Features**

- Separate Source and Sink Pin Up to Typical 7 Apr

- TTL and MOS Compatible Logic Inputs

- Source and Sink typical 7A peak Current

- 13V to 35V Output Supply Voltage Range

- Under Voltage Lockout (UVLO)

- 2500V<sub>RMS</sub> Input to Output Isolation

- Active Shut Down (ASD) and Under Voltage Lockout (UVLO)

- CMTI value of 150 kV/µs

# **Applications**

- Switched-Mode Power Supplies

- Industrial Motor Drivers

- Industrial Power Supplies

# **Description**

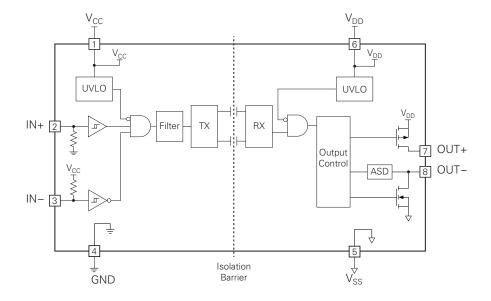

The IX3407B is a galvanically isolated, single-channel gate driver that provides a typical 7A peak source and sink output current on separate output pins. Galvanic input to output isolation is provided by isolation technique where low voltage transmitter die and high voltage receiver die are isolated by integrated high voltage capacitors.

Logic inputs tolerant to input voltages up to  $V_{\rm CC}$  employ TTL voltage thresholds to support a wide range of control logic devices powered by as low as 3.3V.

Protection is provided for both the input and output sides by Under Voltage Lockout (UVLO) circuitry. Additionally, an active shutdown feature protects the power transistor by pulling OUT– low in the event of an output side voltage supply loss.

# **Approvals**

• UL 1577 Recognized Component: File E546287

# **Ordering Information**

| Part Number | Description                         |

|-------------|-------------------------------------|

| IX3407BTR   | SOIC-WB 8 Tape and Reel (1000/Reel) |

# **IX3407B Block Diagram**

| 1 |      | ecifications                                      |   |

|---|------|---------------------------------------------------|---|

|   |      | Package Pinout                                    |   |

|   |      | Pin Description                                   |   |

|   |      | Absolute Maximum Ratings                          |   |

|   |      | Recommended Operating Conditions                  |   |

|   | 1.5  | Electrical Characteristics                        |   |

|   |      | 1.5.1 Input Side Supply Voltage: V <sub>CC</sub>  |   |

|   |      | 1.5.2 Output Side Supply Voltage: V <sub>DD</sub> |   |

|   |      | 1.5.3 Logic Inputs (IN+ and IN-)                  |   |

|   |      | 1.5.4 Gate Driver Outputs                         |   |

|   |      | 1.5.6 Gate Driver Active Shut Down                |   |

|   | 16   | Timing Characteristics                            |   |

|   |      | Thermal Characteristics                           |   |

|   |      | Power Ratings.                                    |   |

|   | 1.9  | Safety and Insulation Rating                      |   |

|   | 1.0  | 1.9.1 Safety Related Certifications               |   |

|   |      | 1.9.2 Insulation Specifications                   |   |

|   |      | 1.9.3 Safety Limiting Values                      |   |

|   | 1.10 | Test Diagrams                                     |   |

|   |      |                                                   |   |

| 2 | Fun  | nctional Description                              | 3 |

|   | 2.1  | Power Supplies                                    | 3 |

|   |      | Logic Inputs (IN+, IN-)                           |   |

|   |      | Gate Drive Outputs (OUT+ and OUT-)                |   |

|   |      | Short Circuit Clamping                            |   |

|   | 2.5  | Protection                                        |   |

|   |      | 2.5.1 Under Voltage Lockout (UVLO)                |   |

|   |      | 2.5.2 Active Shut Down                            | ) |

| 3 | Dor  | formance Data                                     | 1 |

| 3 | rei  | ioimance Data                                     | I |

| 4 | Ma   | nufacturing Information14                         | 1 |

|   | 4.1  | Moisture Sensitivity                              | 1 |

|   |      | ESD Sensitivity.                                  |   |

|   |      | Soldering Profile                                 |   |

|   |      | Board Wash                                        |   |

|   | 4.5  | Mechanical Dimensions 15                          |   |

|   |      | 4.5.1 SOIC-WB 8                                   |   |

|   |      | 4.5.2 Tape and Reel Packaging                     |   |

# 1 Specifications

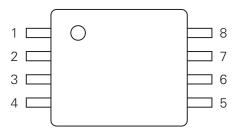

# 1.1 Package Pinout

# 1.2 Pin Description

| Pin | Name            | Pin<br>Type | Description                                  |

|-----|-----------------|-------------|----------------------------------------------|

| 1   | V <sub>CC</sub> | Power       | Input side positive supply voltage           |

| 2   | IN+             | Input       | Non-inverting input                          |

| 3   | IN-             | Input       | Inverting input                              |

| 4   | GND             | Power       | Input side ground                            |

| 5   | V <sub>SS</sub> | Power       | Output side (Driver) supply return           |

| 6   | V <sub>DD</sub> | Power       | Output side (Driver) positive supply voltage |

| 7   | OUT+            | Output      | Driver current source output                 |

| 8   | OUT-            | Output      | Driver current sink output                   |

# 1.3 Absolute Maximum Ratings

Unless otherwise specified, input side voltages are with respect to GND, output side voltages are with respect to  $V_{SS}$ , and electrical ratings are over the operational ambient temperature range.

| Parameter                                              | Cumahal          | Va                     | lue                                       | Units |

|--------------------------------------------------------|------------------|------------------------|-------------------------------------------|-------|

| rarameter                                              | Symbol           | Minimum                | Maximum                                   | Units |

| Output side supply voltage                             | $V_{DD}$         | -0.3                   | +40                                       |       |

| Driver output voltages (OUT+, OUT-)                    | V <sub>OUT</sub> | -0.3                   | $V_{DD} + 0.3$                            | V     |

| Input side supply voltage                              | V <sub>CC</sub>  | -0.3                   | +18                                       | V     |

| Logic input voltages (IN+, IN-)                        | V <sub>IN</sub>  | V <sub>GND</sub> - 0.3 | <sub>ID</sub> - 0.3 V <sub>CC</sub> + 0.3 |       |

| Junction temperature                                   | $T_J$            | -50                    | 150                                       | °C    |

| Storage temperature                                    | T <sub>STG</sub> | -50                    | 150                                       |       |

| Power Dissipation <sup>1</sup> (T <sub>A</sub> =25 °C) |                  |                        |                                           |       |

| Package total                                          | P <sub>tot</sub> | _                      | 1250                                      | mW    |

| ESD rating (Human Body Model) <sup>2</sup>             | V <sub>ESD</sub> | _                      | ±2                                        | kV    |

<sup>&</sup>lt;sup>1</sup> Dependent on PCB layout and heat dissipation design. Reference the thermal impedance evaluation PCB layout shown in "Figure 2 Thermal Characterization PCB Layout" on page 6.

Absolute Maximum Ratings are stress ratings. Stresses in excess of these limits or operation at these limits for extended periods of time can cause permanent damage to the device.

<sup>&</sup>lt;sup>2</sup> Reference JEDEC JS-001-2017.

#### 1.4 Recommended Operating Conditions

Input side voltages are referenced to GND and output side voltages are referenced to V<sub>SS</sub>.

| Parameter                                  | Symbol          | Val     | ue              | Units  |  |

|--------------------------------------------|-----------------|---------|-----------------|--------|--|

| Farameter                                  | Symbol          | Minimum | Maximum         | Offics |  |

| Output side (Driver) supply voltage        | $V_{DD}$        | 13      | 35              |        |  |

| Input side supply voltage                  | V <sub>CC</sub> | 3.1     | 17              | V      |  |

| Logic input voltages IN+, IN-              | V <sub>IN</sub> | 0       | V <sub>CC</sub> |        |  |

| Switching frequency                        | f <sub>SW</sub> | _       | 1               | MHz    |  |

| Ambient temperature                        | T <sub>A</sub>  | -40     | 125             | °C     |  |

| Common Mode Transient Immunity (at 700V) * | CMTI            | 150     | _               | kV/μs  |  |

<sup>\*</sup> Parameter is not subject to production test - verified by design/characterization.

#### 1.5 Electrical Characteristics

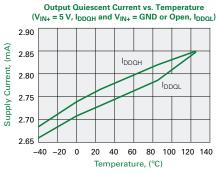

Unless otherwise noted, performance characteristics are specified at:  $V_{CC} = 5V$ ,  $V_{DD} = 15V$ ,  $V_{IN-} = GND$ , and  $-40\,^{\circ}C \le T_{A} \le +125\,^{\circ}C$ . Input side parameters and conditions are referenced to GND with the output side parameters being referenced to  $V_{SS}$ . Output "OUT" is OUT+ connected to OUT-.

Typical values are characteristic of the device at  $T_A = 25$  °C and are the result of engineering evaluations. They are provided for informational purposes only and are not part of the manufacturing testing requirements.

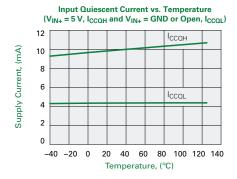

# 1.5.1 Input Side Supply Voltage: V<sub>CC</sub>

| Parameter                | Conditions                     | Cymbol                |         | Units   |         |       |

|--------------------------|--------------------------------|-----------------------|---------|---------|---------|-------|

| Farameter                | Conditions                     | Symbol                | Minimum | Typical | Maximum | Units |

| Quiescent supply current |                                |                       |         |         |         |       |

| OUT = High               | $V_{IN+}=V_{CC}$               | I <sub>CCQH</sub>     | _       | 11.6    | 18.7    | mA    |

| OUT = Low                | V <sub>IN+</sub> = GND or Open | I <sub>CCQL</sub>     | _       | 5.35    | 7.4     | IIIA  |

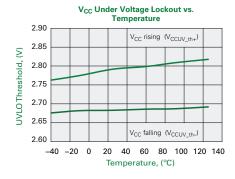

| UVLO rising threshold    | V <sub>CC</sub> rising         | V <sub>CCUV_th+</sub> | 2.65    | 2.83    | 3.0     | V     |

| UVLO falling threshold   | V <sub>CC</sub> falling        | V <sub>CCUV_th-</sub> | 2.58    | 2.73    | _       | V     |

| UVLO hysteresis          | _                              | V <sub>CCUV_hys</sub> | _       | 95      | _       | mV    |

#### 1.5.2 Output Side Supply Voltage: V<sub>DD</sub>

| carbarcarac cabbil       | טט ט                          |                   |         |         |         |        |  |

|--------------------------|-------------------------------|-------------------|---------|---------|---------|--------|--|

| Parameter                | Conditions                    | Cymbal            |         | Units   |         |        |  |

| raidilletei              | Conditions                    | Symbol            | Minimum | Typical | Maximum | Oilles |  |

| Quiescent supply current |                               |                   |         |         |         |        |  |

| OUT = High               | $V_{IN+} = V_{CC}$            | I <sub>DDQH</sub> | _       | 2.5     | 4       | - mA   |  |

| OUT = Low                | V <sub>IN+</sub> =GND or Open | I <sub>DDQL</sub> | _       | 2.35    | 3.8     | IIIA   |  |

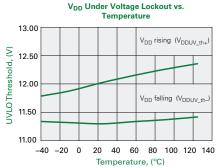

| UVLO rising threshold    | V <sub>DD</sub> rising        | $V_{DDUV\_th+}$   | 11.7    | 12.3    | 13      | \/     |  |

| UVLO falling threshold   | V <sub>DD</sub> falling       | $V_{DDUV\_th-}$   | 10.5    | 11.4    | _       | \ \    |  |

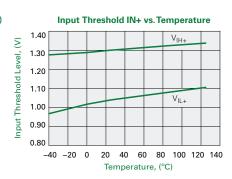

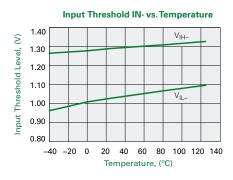

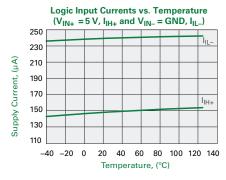

#### 1.5.3 Logic Inputs (IN+ and IN-)

| Parameter           | Conditions           | Cumbal                             |         | Units   |         |                                       |

|---------------------|----------------------|------------------------------------|---------|---------|---------|---------------------------------------|

| rarameter           | Conditions           | Symbol                             | Minimum | Typical | Maximum | Units                                 |

| Input voltage level |                      |                                    |         |         |         |                                       |

| Logic high          |                      | V <sub>IH+</sub> , V <sub>IH</sub> | 2       | _       | _       | \/                                    |

| Logic low           | _                    | $V_{\text{IL+,}}V_{\text{IL-}}$    | _       | _       | 0.8     | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |

| Input current       |                      |                                    |         |         |         |                                       |

| IN+ High            | $V_{IN+} = V_{CC}$   | I <sub>IH+</sub>                   | _       | 160     | 260     |                                       |

| IN- Low             | V <sub>IN</sub> =GND | I <sub>IL</sub>                    | _       | 250     | 360     | - μΑ                                  |

#### 1.5.4 Gate Driver Outputs

| Parameter                      | Conditions                                       | Symbol          | Value                  |         |         | Units          |

|--------------------------------|--------------------------------------------------|-----------------|------------------------|---------|---------|----------------|

| raiailletei                    | Conditions                                       | Syllibol        | Minimum                | Typical | Maximum | Units          |

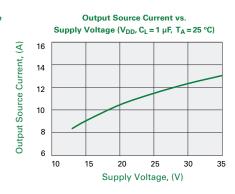

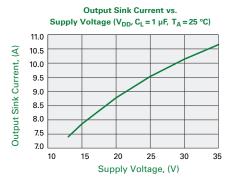

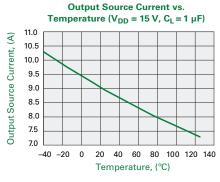

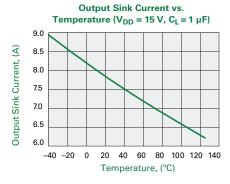

| Peak output current *          |                                                  |                 |                        |         |         |                |

| High level (OUT = High) source | $V_{IN+} = V_{CC}$ , 1 µF load capacitor         | I <sub>OH</sub> | 4                      | 7       | _       | ^              |

| Low level (OUT = Low) sink     | $V_{IN+} = GND$                                  | I <sub>OL</sub> | 4                      | 7       | _       | A <sub>P</sub> |

| Output voltage                 |                                                  |                 |                        |         |         |                |

| High level                     | $V_{IN+} = V_{CC}$ , $I_{OUT+} = -100 \text{mA}$ | V <sub>OH</sub> | V <sub>DD</sub> - 0.14 | _       | _       | V              |

| Low level                      | $V_{IN+} = GND$ , $I_{OUT-} = 100 \text{ mA}$    | V <sub>OL</sub> | _                      | _       | 0.13    | V              |

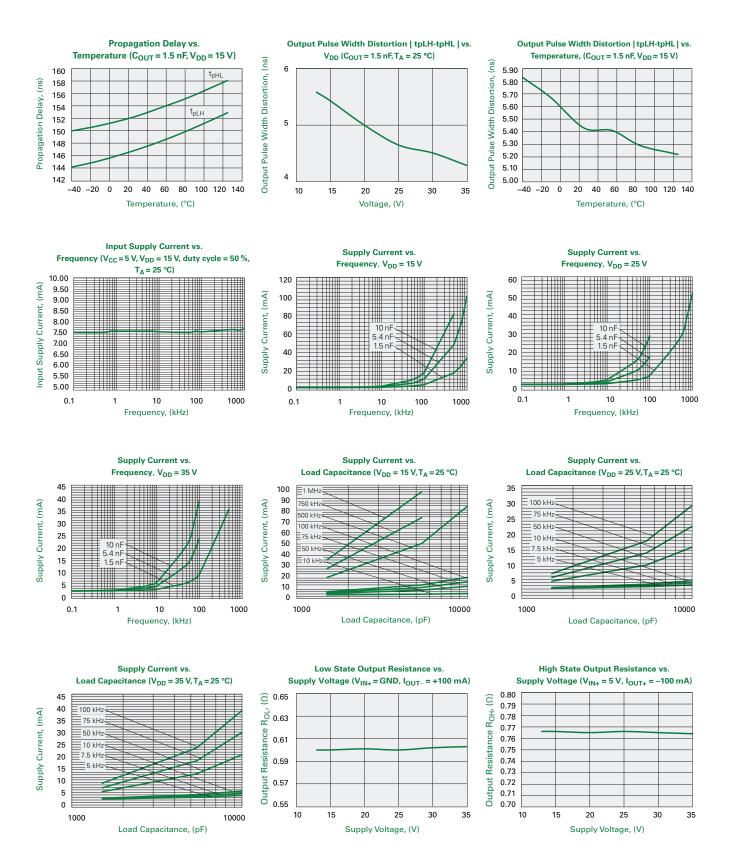

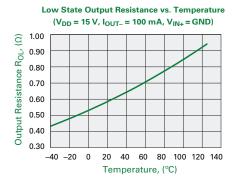

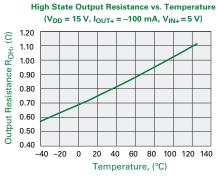

| On-resistance                  |                                                  |                 |                        |         |         |                |

| OUT+                           | $V_{IN+} = V_{CC}$ , $I_{OUT+} = -100 \text{mA}$ | $R_{OH}$        | _                      | 0.75    | 1.4     | Ω              |

| OUT-                           | $V_{IN+} = GND$ , $I_{OUT-} = 100 \text{ mA}$    | R <sub>OL</sub> | _                      | 0.63    | 1.3     | 2.2            |

<sup>\*</sup> Parameter is not subject to production test - verified by design/characterization.

# 1.5.5 OUT+ Short Circuit Clamping

| Parameter                                                | Conditions                                                                                  | Symbol                |         | Units   |         |        |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------|---------|---------|---------|--------|

| raiailletei                                              |                                                                                             |                       | Minimum | Typical | Maximum | Oilles |

| Clamping voltage (V <sub>OUT+</sub> - V <sub>DD</sub> )* | $V_{IN+} = V_{CC}$ , (OUT+ = High)<br>$I_{OUT+} = 500 \text{ mA}$ , $t \le 10 \mu \text{s}$ | V <sub>OUT+_CLP</sub> | _       | 0.5     | 1       | V      |

<sup>\*</sup> Parameter is not subject to production test - verified by design/characterization.

#### 1.5.6 Gate Driver Active Shut Down

| Parameter                             | Conditions                                    | Symbol                 |         | Value   |         | Units |

|---------------------------------------|-----------------------------------------------|------------------------|---------|---------|---------|-------|

| Faianietei                            | Conditions                                    | Зуппьог                | Minimum | Typical | Maximum | Units |

| Active shut down voltage <sup>1</sup> | V <sub>DD</sub> =Open, I <sub>OUT</sub> =0.7A | V <sub>OUTASD_th</sub> | _       | 2.6     | 3.35    | V     |

$<sup>^{1}</sup>$  Referenced to  $V_{SS}$ .

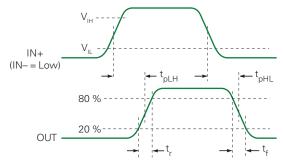

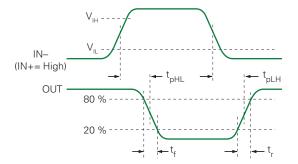

# 1.6 Timing Characteristics

| Parameter                                           | Conditions                                           | Cumhal            | Value   |         |         | Units  |

|-----------------------------------------------------|------------------------------------------------------|-------------------|---------|---------|---------|--------|

| rarameter                                           | Conditions                                           | Symbol            | Minimum | Typical | Maximum | Ullits |

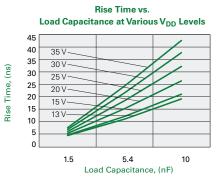

| Propagation delay time                              |                                                      |                   |         |         |         |        |

| Turn-on                                             | C <sub>OUT</sub> = 1 nF                              | t <sub>pLH</sub>  | _       | 154     | 247     |        |

| Turn-off                                            |                                                      | t <sub>pHL</sub>  | _       | 162     | 261     |        |

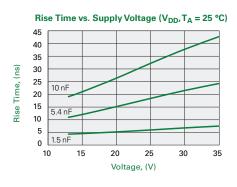

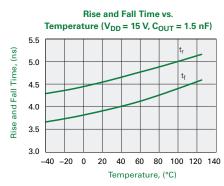

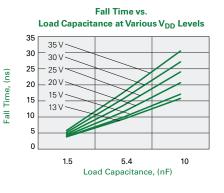

| Turn-on rise time (20 % to 80 %)                    | C _1pE                                               | t <sub>r</sub>    | _       | 10      | 20      | ne     |

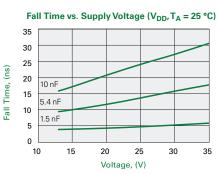

| Turn-off fall time (20 % to 80 %)                   | $C_{OUT} = 1 \text{ nF}$                             | t <sub>f</sub>    | _       | 10      | 20      | ns     |

| Output pulse width distortion $ t_{pLH} - t_{pHL} $ | $C_{OUT} = 1 \text{ nF, } T_A = 25 ^{\circ}\text{C}$ | PWD               | _       | 7.5     | 27      |        |

| Input pulse width suppression                       | OUT = Open                                           | PW <sub>min</sub> | _       | _       | 130     |        |

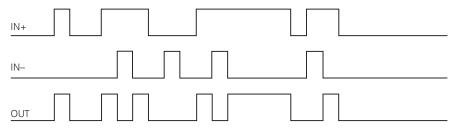

# Figure 1 Timing Waveforms

<sup>\*</sup> Minimum Logic input pulse width 130 ns

# 1.7 Thermal Characteristics

| Parameter           | Symbol               | Rating | Units |

|---------------------|----------------------|--------|-------|

| Thermal impedance   |                      |        |       |

| Junction to Ambient | R <sub>th(j-a)</sub> | 100    | K/W   |

# 1.8 Power Ratings

| Parameter                             | Test Conditions                                | Symbol           | Value |     |         | Unit  |

|---------------------------------------|------------------------------------------------|------------------|-------|-----|---------|-------|

| Faidilletei                           | lest conditions                                | Зуппьог          | Min   | Тур | Max     | Oilit |

| Max. Power Dissipation                | $V_{CC} = 5V$ , $V_{DD} = 15V$ , $IN - = 0V$ , | P <sub>tot</sub> | _     | _   | 1250    |       |

| Max. Power Dissipation by Input Side  | IN+=50 % duty cycle, 440 kHz,                  | P <sub>IN</sub>  | _     | _   | 65.25   | mW    |

| Max. Power Dissipation by Output Side | $C_L = 10 \text{ nF, } T_A = 25 \text{ °C}$    | P <sub>OUT</sub> | _     | _   | 1184.75 |       |

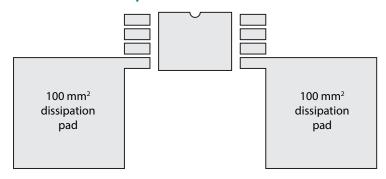

Figure 2 Thermal Characterization PCB Layout

Standard FR4 PCB with 1 oz ( $35 \, \mu m$ ) copper after plating. Pin 4 and pin 5 thermal heat spreading pads are  $100 \, mm^2$ .

# 1.9 Safety and Insulation Rating

# 1.9.1 Safety Related Certifications

|                                                                                               | UL |

|-----------------------------------------------------------------------------------------------|----|

| Recognized under UL 1577 Component Recognition Program,<br>CSA Component Acceptance Notice 5A |    |

| Basic insulaton, 2500V <sub>RMS</sub>                                                         |    |

| File number: E546287                                                                          |    |

#### 1.9.2 Insulation Specifications

| Parameter                   | Test Conditions                                     | Symbol           | Rating | Unit             |

|-----------------------------|-----------------------------------------------------|------------------|--------|------------------|

| UL 1577                     |                                                     |                  |        |                  |

| Withstand isolation voltage | t=60s, RH<50%, T <sub>A</sub> =25°C (Qualification) | V <sub>ISO</sub> | 2500   | \/               |

|                             | t=1s, T <sub>A</sub> =25°C (Production)             |                  | 3000   | V <sub>RMS</sub> |

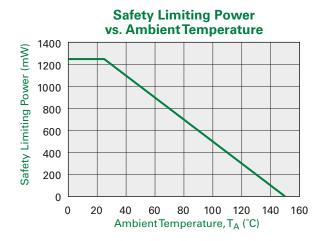

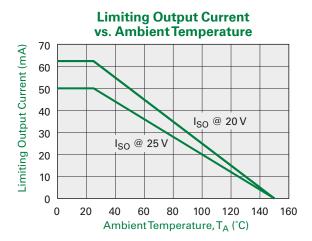

#### 1.9.3 Safety Limiting Values

| Parameter                            | Test Conditions                                                                                                                           | Cumhal          | Value |     |      | Unit  |

|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------|-----|------|-------|

| Farameter                            | lest Conditions                                                                                                                           | Symbol          | Min   | Тур | Max  | Oilit |

|                                      | $\theta_{JA} = 100 \text{ K/W}, V_{DD} = 15 \text{ V}, V_{SS} = -5 \text{ V},$<br>$T_J = 150 ^{\circ}\text{C}, T_A = 25 ^{\circ}\text{C}$ |                 | _     | _   | 62.5 | - mA  |

| Safety output                        | $\theta_{JA} = 100 \text{ K/W}, V_{DD} = 20 \text{ V}, V_{SS} = -5 \text{ V}, T_{J} = 150 ^{\circ}\text{C}, T_{A} = 25 ^{\circ}\text{C}$  | I <sub>SO</sub> | _     | _   | 50   |       |

| Safety input, output, or total power | $\theta_{JA} = 100 \text{ K/W}, V_{DD} = 15 \text{ V}, V_{SS} = -5 \text{ V}, T_{J} = 150 ^{\circ}\text{C}, T_{A} = 25 ^{\circ}\text{C}$  | P <sub>S</sub>  | _     | _   | 1250 | mW    |

| Safety temperature                   | _                                                                                                                                         | T <sub>S</sub>  | _     | _   | 150  | °C    |

# 1.10 Test Diagrams

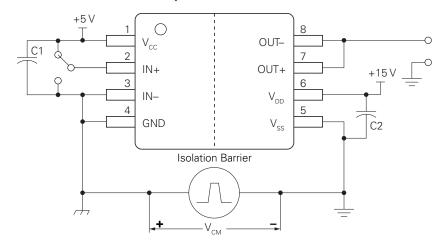

Figure 3 Common Mode Transient Immunity Test Circuit

Note:  $C1 = 1 \, \text{nF}$ ,  $C2 = 1 \, \mu F$  ceramic capacitors. The values of decoupling capacitors depend on application.

# 2 Functional Description

Designed to provide gate drive for high power IGBTs, the IX3407B is well suited for also driving MOSFET and SiC MOSFET gates. Supplying essential protection and control functionality enables straightforward designs, while minimizing design times of low-cost, highly-reliable systems. The proprietary capacitive isolation technique provides 2500V<sub>RMS</sub> of input control logic side to output gate driver side isolation, thereby ensuring driver safe and reliable operation.

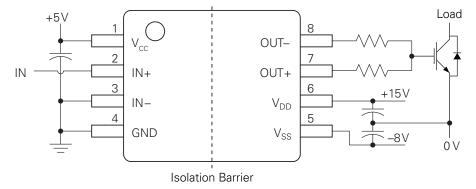

Figure 4 IX3407B Typical Application Circuit

#### 2.1 Power Supplies

As the IX3407B input side is isolated from the driver output side, each side has independent voltage supply and returns (grounds). On the input side, power is supplied by V<sub>CC</sub> and is grounded by the GND pin, while the output side power is supplied by  $V_{DD}$ ; with  $V_{SS}$  being the return.  $V_{SS}$  can be biased to either a 0V ground rail, or a negative voltage supply for IGBT applications. These two output side biasing styles are commonly referred to as unipolar and bipolar respectively. In unipolar mode, V<sub>SS</sub> is at the same potential as V<sub>FF</sub>; the IGBT emitter. For MOSFET applications, V<sub>SS</sub> would be at the same potential as the source voltage.

With bipolar supplies, the driver is operated with a positive supply voltage at the V<sub>DD</sub> pin and a negative supply voltage on the  $V_{SS}$  pin, both with respect to  $V_{EE}$ ; the supply voltage of the IGBT emitter. Typically, applications are operated with  $V_{\rm DD}$  = 15V and  $V_{\rm SS}$  = -8V relative to  $V_{\rm EE}$ , as shown above in Figure 4, the "IX3407B Typical Application Circuit." Using a negative supply can help prevent dynamic turn-on due to the current flowing from the IGBT collector, through the Miller capacitor, to the gate driver OUT- output.

To assure proper startup and behavior when a supply voltage is lost or drops below a preset threshold, each side is equipped with Under Voltage Lockout circuitry.

## 2.2 Logic Inputs (IN+, IN-)

In order to simplify circuit design, the IX3407B provides both non-inverting and inverting inputs using TTL voltage level thresholds and are input voltage tolerant up to the V<sub>CC</sub> supply voltage level. This flexibility allows designing to a wide range of predetermined conditions, or upgrading a preexisting product model with minimal, or no modification to the control logic hardware, or firmware.

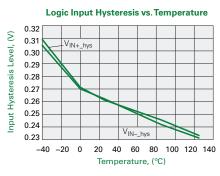

The IN+ and IN- logic inputs control the state of the high-current source and sink driver outputs, OUT+ and OUT- respectively. These TTL voltage level threshold inputs are high-speed Schmitt trigger buffers with a typical 300 mV of hysteresis. To ensure a defined start up behavior, internal resistors pull the non-inverting input IN+ to GND, while the inverting input IN- is pulled up to V<sub>CC</sub>, thereby ensuring the power device is off by pulling its gate down to V<sub>ss</sub>.

Before being passed across the isolation barrier to the output control circuitry, the input side control signal is filtered to ensure high and low logic pulses shorter than the minimum PW<sub>min</sub> specification are rejected. This enables the circuit to operate reliably with very large, or small input signal duty cycles, or when operating in a noisy environment.

Although the IX3407B has two inputs, the gate driver is easily controlled using only one. To configure the driver as non-inverting, tie the IN- input to GND and apply the control signal to IN+. For an inverting driver tie IN+ to V<sub>CC</sub> and apply the control signal to IN-. If using an external resistor to condition the IN+, or IN- high, or low, care must be taken to account for the voltage drop across the internal pull down (IN+) and pull up (IN-) resistors. The resistor values can be calculated with V<sub>CC</sub> = 5V and typical leakage currents listed in 1.5.3 Logic Inputs table. The IN- pull-up resistor is 31.25 k $\Omega$  and IN+ pull-down resistor is 20 k $\Omega$ .

**Table 1: Function Table**

| IN+ | + IN- UVLO 3 OUT+ | IN-             | IN_ UVLO <sup>3</sup> | OUT+ | OUT- | OUT <sup>1</sup> |

|-----|-------------------|-----------------|-----------------------|------|------|------------------|

| ПЧТ |                   | V <sub>cc</sub> | V <sub>DD</sub>       | 0011 | 0011 | 001-             |

| Χ   | X                 | X               | 1                     | Hi-Z | Low  | $V_{SS}$         |

| X   | X                 | 1               | X                     | Hi-Z | Low  | V <sub>SS</sub>  |

| 0 2 | X                 | X               | X                     | Hi-Z | Low  | V <sub>SS</sub>  |

| X   | 1 <sup>2</sup>    | X               | X                     | Hi-Z | Low  | V <sub>SS</sub>  |

| 1   | 0                 | 0               | 0                     | High | Hi-Z | V <sub>DD</sub>  |

<sup>&</sup>lt;sup>1</sup> OUT = OUT+ tied to OUT-.

UVLO = 1: Insufficient supply voltage.

Figure 5 Logic Diagram

Note:  $V_{CC}$  and  $V_{DD}$  power supply UVLO must be off.

#### 2.3 Gate Drive Outputs (OUT+ and OUT-)

The IX3407B gate drive outputs are rated for a minimum peak current of 4A, with a typical peak current of 7A. Independent source (OUT+) and sink (OUT-) outputs enable implementation of low-cost asymmetrical charge and discharge rates of the power device gate, through separate resistors between the driver outputs and the gate. To minimize power losses, an internal dead time prevents output cross conduction.

## 2.4 Short Circuit Clamping

Under conditions where the current through an IGBT begins to rapidly increase, such as when the load short circuits, charge may be transferred from the collector to the gate via the Miller capacitor, causing the gate voltage and subsequently the gate driver output voltage to increase. When the gate driver output voltage exceeds  $V_{\rm DD}$ , the driver's positive voltage supply, an internal circuit clamps the rising voltage. The IX3407B is capable of passing  $500\,\text{mA}$  for  $10\,\mu\text{s}$ . For greater current or durations, an auxiliary external clamp should be provided.

#### 2.5 Protection

The IX3407B provides two forms of protection: Under Voltage Lockout (UVLO), where the driver outputs are held low when either one of the positive voltage supplies is too low, and an Active Shutdown circuit that drives the power transistor off, whenever the output side positive supply is lost and sufficient gate charge persists.

#### 2.5.1 Under Voltage Lockout (UVLO)

As a safety feature, the IX3407B contains UVLO circuitry on both the input-side and the driver (output) side, which monitors the supply voltage of their respective section. They prevent both intentional and false turn-on of the driver output, until the input and output-side supply voltages have attained their minimum required potentials for proper operation. As determined by internally set thresholds. Input control signals are permitted to manage the load only after both UVLO circuits have cleared; until then, output conditioning is independent of the input-control signal and the outputs are held in the off state, which clamps the power transistor gate to the  $\rm V_{SS}$  level. During the off state, the driver is reset forcing OUT+ to a high impedance and OUT- to  $\rm V_{SS}$ . The Function Table illustrates this aspect of the driver's behavior.

Under voltage lockout prevents the driver from unintended biasing of the power transistor gate, thereby preventing the power transistor from being fully or partially turned on. Without UVLO, a partial turn-on can occur whenever the driver side supply voltage is sufficient to initiate conductance through the power transistor, but less than the voltage required to fully turn the power transistor on.

Under voltage lockout will occur during start-up, prior to the power supplies reaching an acceptable operating level, during normal operation, anytime either supply drops below the internally set minimum threshold level and on power-down. Hysteresis is provided to separate the supply

<sup>&</sup>lt;sup>2</sup> Or floating.

<sup>&</sup>lt;sup>3</sup> UVLO=0: Sufficient supply voltage.

rising and falling thresholds, in order to provide continuous operation in the presence of noise and voltage drops in the supplies. While the UVLO hysteresis provides partial immunity to power supply transients, it does not mask large voltage changes in the supplies.

#### 2.5.2 Active Shut Down

As a complement to the Under Voltage Lockout feature, the IX3407B offers an Active-Shut-Down (ASD) mechanism, to drain the IGBT/MOSFET gate charge whenever the driver-side-supply voltage is insufficient to operate the OUT– pull down FET, and excessive gate bias and charge is present at the OUT– pin.

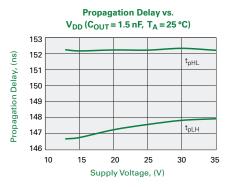

# 3 Performance Data

# 4 Manufacturing Information

#### 4.1 Moisture Sensitivity

All plastic encapsulated semiconductor packages are susceptible to moisture ingression. Littelfuse classifies its plastic encapsulated devices for moisture sensitivity according to the latest revision of the joint industry standard,

IPC/JEDEC J-STD-020, in force at the time of product evaluation. We test all of our products to the maximum conditions set forth in the standard, and guarantee proper operation of our devices when handled according to the limitations and information in that standard as well as to any limitations set forth in the information or standards referenced below.

Failure to adhere to the warnings or limitations as established by the listed specifications could result in reduced product performance, reduction of operable life, and/or reduction of overall reliability.

This product carries a Moisture Sensitivity Level (MSL) classification as shown below, and should be handled according to the requirements of the latest revision of the joint industry standard IPC/JEDEC J-STD-033.

| Device  | Moisture Sensitivity Level (MSL) Classification |  |  |  |

|---------|-------------------------------------------------|--|--|--|

| IX3407B | MSL 3                                           |  |  |  |

## 4.2 ESD Sensitivity

This product is ESD Sensitive, and should be handled according to the industry standard JESD-625.

#### 4.3 Soldering Profile

Provided in the table below is the **IPC/JEDEC J-STD-020** Classification Temperature (T<sub>C</sub>) and the maximum dwell time (T<sub>C</sub>-5°C). The Classification Temperature sets the Maximum Body Temperature allowed for these devices, during reflow soldering processes.

| Device  | Device Classification Temperature (T <sub>c</sub> ) |            | Max Reflow Cycles |

|---------|-----------------------------------------------------|------------|-------------------|

| IX3407B | 260°C                                               | 30 seconds | 3                 |

#### 4.4 Board Wash

Littelfuse recommends the use of no-clean flux formulations. Board washing to reduce, or remove flux residue following the solder reflow process is acceptable, provided proper precautions are taken to prevent damage to the device. These precautions include, but are not limited to: Using a low pressure wash and providing a follow-up bake cycle sufficient to remove any moisture trapped within the device, due to the washing process. Due to the variability of the wash parameters used to clean the board, determination of the bake temperature and duration necessary to remove the moisture trapped within the package is the responsibility of the user (assembler). Cleaning, or drying methods that employ ultrasonic energy may damage the device and should not be used. Additionally, the device must not be exposed to halide flux or solvents.

#### 4.5 Mechanical Dimensions

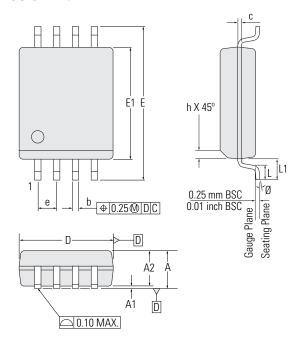

#### 4.5.1 SOIC-WB 8

|        | mm        |      | in        | ch    |  |

|--------|-----------|------|-----------|-------|--|

| SYMBOL | MIN       | MAX  | MIN       | MAX   |  |

| Α      | -         | 2.65 | -         | 0.104 |  |

| A1     | 0.10      | 0.20 | 0.004     | 0.008 |  |

| A2     | 2.25      | 2.45 | 0.089     | 0.096 |  |

| b      | 0.30      | 0.50 | 0.012     | 0.020 |  |

| С      | 0.23      | 0.33 | 0.009     | 0.013 |  |

| D      | 6.30 BSC  |      | 0.248 BSC |       |  |

| Е      | 10.30 BSC |      | 0.406 BSC |       |  |

| E1     | 7.50 BSC  |      | 0.295     | 5 BSC |  |

| е      | 1.27 BSC  |      | 0.050     | ) BSC |  |

| L      | 0.50      | 0.90 | 0.020     | 0.035 |  |

| L1     | 1.40      | REF  | 0.055 REF |       |  |

| h      | 0.25      | 0.75 | 0.010     | 0.030 |  |

| Ø      | 0°        | 8°   | 0°        | 8°    |  |

#

#### NOTES:

- 1. Controlling dimension: millimeter

- Dimension "D" does not include mold flash, protrusions or gate burrs.Mold flash, protrusions and gate burrs shall not exceed 0.15 mm per side.

- Dimension "E1" does not include inter-lead flash or protrusions. Inter-lead flash and protrusions shall not exceed 0.25 mm per side.

NO measurement required.

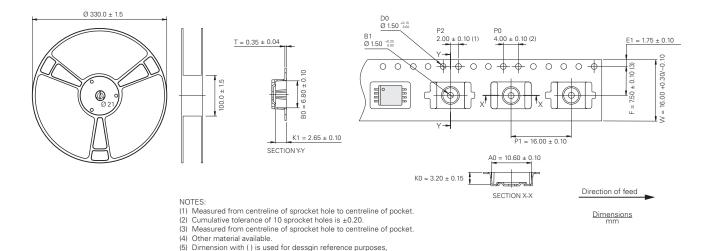

# 4.5.2 Tape and Reel Packaging

Disclaimer Notice - Information furnished is believed to be accurate and reliable. However, users should independently evaluate the suitability of and test each product selected for their own applications. Littelfuse products are not designed for, and may not be used in, all applications. Read complete Disclaimer Notice at https://www.littelfuse.com/disclaimer-electronics