# LITELINK™ III Application Circuit Calculations

### 1. Introduction

IXYS IC Division recommends using the application circuits provided in LITELINK III (CPC5620 and CPC5621) datasheet and application notes. These circuits have been designed and tested to comply with applicable regulatory requirements. It is possible, however, to adjust the values of certain application circuit components to achieve specific results.

This application note provides the equations used by our engineers to arrive at the recommended application circuit values. With this information you will be able to make slight adjustments. Changes to the provided recommendations may yield an application circuit that does not meet safety and other regulatory or performance requirements.

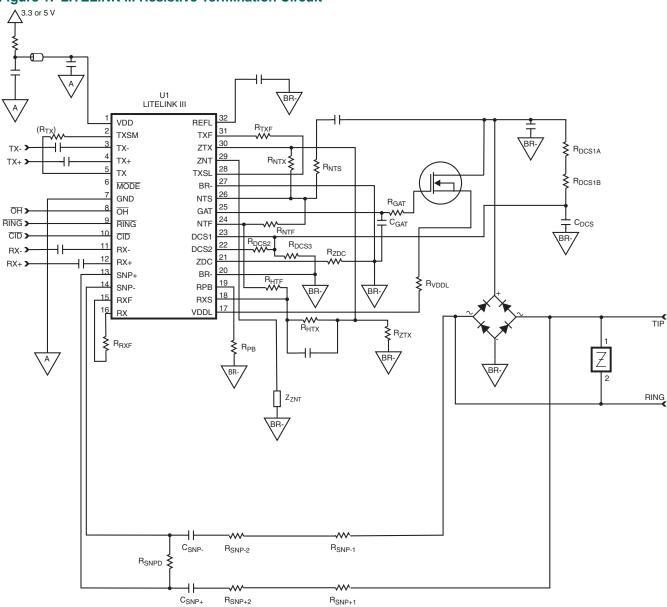

Mnemonics in the equations refer to components in the standard LITELINK III application circuit shown in Figure 1.

Figure 1. LITELINK III Resistive Termination Circuit

# 2. LITELINK III DC Characteristic Equations

The following equations describe the dc operating characteristics of the telephone line side of LITELINK III and LITELINK III dc requirements for the loop.

### 2.1 Loop Current Limit

$R_{ZDC}$ ,  $R_{ZTX}$ , and  $R_{ZNT}$  determine the off-hook loop current.

$$I_{CL} = \left[\frac{1V}{R_{ZDC}}\right] + \frac{0.625V}{R_{ZTX} \parallel R_{ZNT}} + 5.5 \text{ mA}$$

Adjust the value of  $R_{ZDC}$  to modify the loop current limit characteristics.

### 2.2 Minimum Line Operating Current

The portion of the LITELINK on the telephone line side of the internal optical barrier is powered from the phone line, and requires a minimum operating current from the phone line to work. This value is calculated as follows:

$$I_{MIN} = \frac{0.625V}{R_{ZTX} || R_{ZNT}} + 5.5 \text{ mA}$$

# 2.3 DC Line Current Versus Line Voltage Characteristics

#### 2.3.1 Minimum Loop Voltage

The minimum loop voltage with which LITELINK III will operate is defined as:

$$V_{LINE} \ge V_{BRIDGE} + V_{PEAK} + 3.25V$$

where  $V_{\mbox{\footnotesize{PEAK}}}$  is the peak value of the signal on the line.

# 2.3.2 Line Current Programming Resistor Ratio Requirement

LITELINK III requires the following circuit ratio for operation:

$$\frac{R_{DCS\,1} \, \|\, R_{DCS\,3}}{(R_{DCS\,2} + R_{DCS\,1} \, \|\, R_{DCS\,3})} \approx \frac{1}{1.2}$$

Failure to meet this requirement will result in poor error cancellation within LITELINK III.

Note:  $R_{DCS3}$  is not needed in circuits where ratio constraint described above is met.  $R_{DCS3}$  is not used in IXYS Integrated Circuits Division application circuits where the error introduced is negligible.

# 2.4 DC I-V With R<sub>DCS3</sub>

The following equations describe loop current and voltage characteristics when R<sub>DCS3</sub> is used and when the constraint in "Line Current Programming Resistor Ratio Requirement" on page 4 has been met.

$$I_{LINE} = \frac{\left[ (V_{LINE} - V_{BRIDGE}) \left( \frac{R_{DCS\,2} \| R_{DCS\,3}}{R_{DCS\,1} + R_{DCS\,2} \| R_{DCS\,3}} \right) \right] - 0.5V}{R_{ZDC}} + \frac{0.625V}{R_{ZTX} \| R_{ZNT}} + 5.5 \text{ mA}$$

$$V_{LINE} = V_{BRIDGE} + \left[ \frac{(R_{DCS\,1} + R_{DCS\,2} \parallel R_{DCS\,3})}{R_{DCS\,2} \parallel R_{DCS\,3}} \right] \left[ 0.5V + \left( I_{LINE} - \frac{0.625V}{R_{ZTX} \parallel R_{ZNT}} - 5.5mA \right) (R_{ZDC}) \right]$$

### 2.5 DC I-V Without RDCS3

The following equations describe loop current and voltage characteristics when R<sub>DCS3</sub> is not used and when the constraint in "Line Current Programming Resistor Ratio Requirement" on page 4 has been met.

$$I_{LINE} = \frac{\left[ (V_{LINE} - V_{BRIDGE}) \left( \frac{R_{DCS\,2}}{R_{DCS\,1} + R_{DCS\,2}} \right) \right] - 0.5V}{R_{ZDC}} + \frac{0.625V}{R_{ZTX} \parallel R_{ZNT}} + 5.5 \text{mA}$$

$$V_{LINE} = V_{BRIDGE} + \left[ \frac{(R_{DCS\,1} + R_{DCS\,2})}{R_{DCS\,2}} \right] \left[ 0.5V + \left( I_{LINE} - \frac{0.625V}{R_{ZTX} \parallel R_{ZNT}} - 5.5 \,\text{mA} \right) (R_{ZDC}) \right]$$

### 2.6 DC Line Current without R<sub>DCS3</sub> (in General)

The following equation describes loop current characteristics in general terms as used in the recommended application circuit, where RDCS3

is not used and without regard to the constraint in "Line Current Programming Resistor Ratio Requirement" on page 4.

$$I_{LINE} = \frac{\frac{(V_{LINE} - V_{BRIDGE})(R_{DCS2})}{(R_{DCS1} + R_{DCS2})} - \frac{(1.2)(R_{DCS1})(0.5V)}{(R_{DCS1} + R_{DCS2})} + (V_{TH}) \left[ \frac{(1.2)(R_{DCS1})}{(R_{DCS1} + R_{DCS2})} - 1 \right]}{R_{ZDC} + (R_S) \left[ \frac{(1.2)(R_{DCS1})}{R_{DCS1} + R_{DCS2}} - 1 \right]} + \frac{0.625V}{R_{ZTX} \parallel R_{ZNT}} + 5.5 \text{ mA} \right]$$

Where:

$V_{TH} \sim 0.7 \text{ V } (\pm 0.2 \text{ V})$ , and where

$R_S \sim 6~\Omega~(\pm~2~\Omega)$ .  $R_S$  is an on-chip resistance.

# 3. LITELINK III AC Characteristic Equations

### 3.1 Ring Detection Threshold

The Ring detector threshold describes the input condition at which the LITELINK III ring detector output will change states. Ring detection threshold and display feature (caller-ID) signal gain (see "Display Feature Signal Gain" on page 6) are areas where customization of the LITELINK III application circuits is supported by IXYS IC Division. Ring detection threshold is determined by the following equation:

$$V_{RINGPK} = \left(\frac{750 \text{mV}}{R_{SNPD}}\right) \left[ (2R_{SNP} + R_{SNPD})^2 + \frac{1}{\left[ (\pi \cdot f_{RING})(C_{SNOOP}) \right]^2} \right]^{1/2}$$

For more information on setting the ring detection threshold see the LITELINK datasheets and IXYS IC Division's application note spreadsheet AN-117, Customize LITELINK Caller ID Gain and Ring Detect Voltage Threshold.

### 3.2 Display Feature Signal Gain

Display feature (caller-ID) signal gain and ring detection threshold (see "Ring Detection Threshold" on page 6) are areas where customization of the LITELINK III application circuits is supported by IXYS IC Division. Display feature signal gain can be calculated for both differential and single-ended circuit applications using the following equations:

#### 3.2.1 Differential Display Feature Gain

Between RX+ and RX-.

$$\mathsf{GAIN}_{\mathsf{CID}} = \frac{\mathsf{6R}_{\mathsf{SNPD}}}{\left[ (2\mathsf{R}_{\mathsf{SNP}} + \mathsf{R}_{\mathsf{SNPD}}) + \frac{1}{\left[ (\pi \bullet \mathsf{f}_{\mathsf{CID}}) (\mathsf{C}_{\mathsf{SNOOP}}) \right]^2} \right]^{1/2}}$$

Where  $R_{SNP+} = R_{SNP-} = R_{SNP}$ .

#### 3.2.2 Differential Display Feature Gain (dB)

Between RX+ and RX-.

$$GAIN (dB)_{CID} = 20log \left[ \frac{6R_{SNPD}}{\left[ (2R_{SNP} + R_{SNPD}) + \frac{1}{\left[ (\pi \cdot f_{CID})(C_{SNOOP}) \right]^2} \right]^{1/2}} \right]$$

#### 3.2.3 Single-ended Display Feature Gain

Between RX+ and RX-.

$$GAIN_{CID} = \frac{3R_{SNPD}}{\left[ (2R_{SNP} + R_{SNPD}) + \frac{1}{\left[ (\pi \cdot f_{CID})(C_{SNOOP}) \right]^2} \right]^{1/2}}$$

Where  $R_{SNP+} = R_{SNP-} = R_{SNP-}$

#### 3.2.4 Single-ended Display Feature Gain (dB)

Between RX+ and RX-.

$$GAIN (dB)_{CID} = 20log \left[ \frac{3R_{SNPD}}{\left[ (2R_{SNP} + R_{SNPD}) + \frac{1}{\left[ (\pi \cdot f_{CID})(C_{SNOOP}) \right]^2} \right]^{1/2}} \right]$$

For more information on setting the display feature gain see the LITELINK datasheets and the application note spreadsheet AN-117, Customize LITELINK Caller ID Gain and Ring Detect Voltage Threshold.

# 3.3 Termination Impedance

The following equation represents the ac impedance on the telephone loop represented by LITELINK III. It defines the  $\Delta V/\Delta I$  of LITELINK III.

$$Z_{TERMINATION} = \left(\frac{R_{NTS}}{R_{NTF}}\right)(Z_{ZNT})$$

### 3.4 Transmit Insertion Loss (4-Wire to 2-Wire)

#### 3.4.1 DC Transmit Ratio Constraint

$$R_{TXF} = (0.749)(R_{TX})$$

The following circuit constraint must be met for correct operation of LITELINK III.

#### 3.4.2 Insertion Loss to Line

LITELINK III transmit gain can be calculated as:

$$GAIN_{TX} = \left(\frac{1}{1.5}\right) \left(\frac{R_{TXF}}{R_{TX}}\right) \left(\frac{\frac{Z_{ZNT}}{Z_{ZTX}} + \frac{R_{NTF}}{R_{NTX}}}{\frac{Z_{ZNT}}{Z_{LINF}} + \frac{R_{NTF}}{R_{NTS}}}\right)$$

LITELINK III transmit insertion loss (in decibels) can be calculated as:

$$IL_{TX_{dB}} = -20log \left[ \left( \frac{1}{1.5} \right) \left( \frac{R_{TXF}}{R_{TX}} \right) \left( \frac{\frac{Z_{ZNT}}{Z_{ZTX}} + \frac{R_{NTF}}{R_{NTX}}}{\frac{Z_{ZNT}}{Z_{LINE}} + \frac{R_{NTF}}{R_{NTS}}} \right) \right]$$

### 3.5 Receive Insertion Loss (2-Wire to 4-Wire)

#### 3.5.1 DC Receive Ratio Constraint

The following circuit constraint must be met for correct operation of LITELINK III.

$$R_{RXF} = (1.30)(R_{HTX} || R_{HTF})$$

#### 3.5.2 Differential Insertion Loss to RX+/RX-

LITELINK III differential receive gain can be calculated as:

GAIN<sub>RX</sub> =

$$\left(\frac{2}{0.65}\right)\left(\frac{R_{NTF}}{R_{NTS}}\right)\left(\frac{R_{RXF}}{R_{HTF}}\right)$$

LITELINK III differential receive insertion loss (in decibels) can be calculated as:

$$IL_{RX_{dB}} = -20log\left[\left(\frac{2}{0.65}\right)\left(\frac{R_{NTF}}{R_{NTS}}\right)\left(\frac{R_{RXF}}{R_{HTF}}\right)\right]$$

# 3.5.3 Single-ended Insertion Loss to RX+ or RX-

LITELINK III single-ended receive gain can be calculated as:

GAIN<sub>RX</sub> =

$$\left(\frac{1}{0.65}\right)\left(\frac{R_{NTF}}{R_{NTS}}\right)\left(\frac{R_{RXF}}{R_{HTF}}\right)$$

LITELINK III single-ended receive insertion loss (in decibels) can be calculated as:

$$\mathsf{IL}_{\mathsf{RX}_{\mathsf{dB}}} = -20\mathsf{log}\bigg[\bigg(\frac{1}{0.65}\bigg)\bigg(\frac{\mathsf{R}_{\mathsf{NTF}}}{\mathsf{R}_{\mathsf{NTS}}}\bigg)\bigg(\frac{\mathsf{R}_{\mathsf{RXF}}}{\mathsf{R}_{\mathsf{HTF}}}\bigg)\bigg]$$

### 3.6 Trans-Hybrid Loss (4-Wire Return Loss)

The hybrid network is also known as the 2-to-4 wire converter. The loss from transmit path to receive path

is known as trans-hybrid loss, measured in decibels. LITELINK III trans-hybrid loss can be calculated as:

$$\mathsf{THL}_{\mathsf{dB}} \, = \, -20 \mathsf{log} \Bigg[ \bigg( \frac{1}{0.65} \bigg) \Bigg[ \bigg| \bigg( \frac{1}{1.5} \bigg) \bigg( \frac{\mathsf{R}_{\mathsf{RXF}}}{\mathsf{R}_{\mathsf{HTF}}} \bigg) \bigg( \frac{\mathsf{R}_{\mathsf{TXF}}}{\mathsf{R}_{\mathsf{TX}}} \bigg) \bigg( 1 - \frac{\mathsf{R}_{\mathsf{NTF}}}{\mathsf{R}_{\mathsf{NTX}}} \bigg) + \mathsf{GAIN}_{\mathsf{TX}} \bigg( \frac{\mathsf{R}_{\mathsf{NTF}}}{\mathsf{R}_{\mathsf{NTS}}} \bigg) \bigg( \frac{\mathsf{R}_{\mathsf{RXF}}}{\mathsf{R}_{\mathsf{HTX}}} \bigg) \bigg] \Bigg] \Bigg]$$

# 4. Reference Designations

The following table connects reference designators for circuit elements used in this application note with chip pin mnemonics. See also the schematic "LITELINK III Resistive Termination Circuit" on page 3.

| Designator        | Connects Pin | То       |

|-------------------|--------------|----------|

| Z <sub>ZNT</sub>  | ZNT          | BR-      |

| R <sub>NTF</sub>  | NTF          | pin NTS  |

| Z <sub>ZTX</sub>  | ZTX          | BR-      |

| R <sub>NTX</sub>  | ZTX          | pin NTS  |

| R <sub>HTF</sub>  | NTF          | pin RXSL |

| R <sub>RXF</sub>  | RX           | pin RXF  |

| R <sub>TXF</sub>  | TXF          | pin TXS  |

| R <sub>TX</sub>   | TX           | pin TXSM |

| R <sub>ZDC</sub>  | ZDC          | BR-      |

| R <sub>DCS1</sub> | BR+          | pin DCS1 |

| R <sub>DCS1</sub> | DCS1         | pin DCS2 |

| R <sub>DCS3</sub> | DCS1         | BR-      |

# 5. LITELINK Design Resources

### **5.1 IXYS IC Division Design Resources**

www.ixysic.com has a wealth of information useful for designing with LITELINK, including application notes and reference designs that already meet all applicable regulatory requirements. LITELINK data sheets also contains additional application and design information. See the following links:

#### LITELINK datasheets and reference designs

Application note AN-117 Customize Caller-ID Gain and Ring Detect Voltage Threshold for CPC5610/11

Application note AN-146, **Guidelines for Effective LITELINK Designs**

Application note AN-152 LITELINK II to LITELINK III Design Conversion

Application note AN-155 Understanding LITELINK Display Feature Signal Routing and Applications

#### For additional information please visit our website at: www.ixysic.com

IXYS Integrated Circuits Division makes no representations or warranties with respect to the accuracy or completeness of the contents of this publication and reserves the right to make changes to specifications and product descriptions at any time without notice. Neither circuit patent licenses nor indemnity are expressed or implied. Except as set forth in IXYS Integrated Circuits Division's Standard Terms and Conditions of Sale, IXYS Integrated Circuits Division assumes no liability whatsoever, and disclaims any express or implied warranty, relating to its products including, but not limited to, the implied warranty of merchantability, fitness for a particular purpose, or infringement of any intellectual property right.

The products described in this document are not designed, intended, authorized or warranted for use as components in systems intended for surgical implant into the body, or in other applications intended to support or sustain life, or where malfunction of IXYS Integrated Circuits Division's product may result in direct physical harm, injury, or death to a person or severe property or environmental damage. IXYS Integrated Circuits Division reserves the right to discontinue or make changes to its products at any time without notice.

Specification: AN-158-R03 ©Copyright 2014, IXYS Integrated Circuits Division All rights reserved. Printed in USA. 4/15/2014